# CY27C64

# 8K x 8 EPROM

#### Features

- CMOS for optimum speed/power

- Windowed for reprogrammability

- High speed

- -0 ns (commercial)

- Low power

- -40 mW (commercial)

- 30 mW (military)

- Super low standby power

- -Less than 85 mW when deselected

- EPROM technology 100% programmable

- + 5V  $\pm 10\%$  V  $_{CC},$  commercial and military

- TTL-compatible I/O

#### **Functional Description**

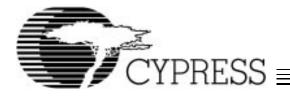

The CY27C64 is a high-performance 8192 word by 8 bit CMOS PROM. When deselected, the CY27C64 automatically

powers down into a low-power standby mode. It is packaged in a 600-mil-wide package. The reprogrammable packages are equipped with an erasure window; when exposed to UV light, these EPROMs are erased and can then be reprogrammed. The memory cells utilize proven EPROM floating-gate technology and byte-wide intelligent programming algorithms.

The EPROM cell requires only 12.5V for the super voltage and low-current requirements allow for gang programming. The EPROM cells allow for each memory location to be tested 100%, as each location is written into, erased, and repeatedly exercised prior to encapsulation. Each EPROM is also tested for AC performance to guarantee that after customer programming, the product will meet DC and AC specification limits.

Reading is accomplished by placing an active LOW signal on  $\overline{OE}$  and  $\overline{CE}$ . The contents of the memory location addressed by the address lines (A<sub>0</sub> through A<sub>12</sub>) will become available on the output lines (O<sub>0</sub> through O<sub>7</sub>).

1. Pins 1 and 17 are common and tied to the die attach pad. They should not be used.

# **Selection Guide**

|                          |            | 27C64-70 | 27C64-90 | 27C64-120 | 27C64-150 | 27C64-200 |

|--------------------------|------------|----------|----------|-----------|-----------|-----------|

| Maximum Access Time (ns) |            | 70       | 90       | 120       | 150       | 200       |

| Maximum Operating        | Commercial | 80       | 80       | 80        | 80        | 80        |

| Current (mA)             | Military   | 100      | 100      | 100       | 100       | 100       |

| Maximum Standby          | Commercial | 15       | 15       | 15        | 15        | 15        |

| Current (mA)             | Military   | 15       | 15       | 15        | 15        | 15        |

## **Maximum Ratings**

| (Above which the useful life may be impaired. For user guide-lines, not tested.) |  |

|----------------------------------------------------------------------------------|--|

| Storage Temperature65°C to +150°C                                                |  |

| Ambient Temperature with<br>Power Applied55°C to +125°C                          |  |

| Supply Voltage to Ground Potential<br>(DIP Pin 28 to Pin 14)0.5V to +7.0V        |  |

| DC Voltage Applied to Outputs<br>in High Z State0.5V to +7.0V                    |  |

| DC Input Voltage3.0V to +7.0V                                                    |  |

| DC Program Voltage                                                               |  |

|                                                                                  |  |

| Static Discharge Voltage<br>(per MIL–STD–883, Method 3015) | > 2001 V                  |

|------------------------------------------------------------|---------------------------|

| Latch–Up Current                                           | > 200 mA                  |

| UV Exposure                                                | 7258 Wsec/cm <sup>2</sup> |

## **Operating Range**

| Range                     | Ambient<br>Temperature | v <sub>cc</sub> |

|---------------------------|------------------------|-----------------|

| Commercial                | 0°C to +70°C           | 5V ± 10%        |

| Industrial <sup>[2]</sup> | –40°C to +85°C         | 5V ± 10%        |

| Military <sup>[3]</sup>   | –55°C to +125°C        | 5V ± 10%        |

## Electrical Characteristics Over the Operating Range<sup>[4,5]</sup>

| Parameter       | Description                                 | Test Conditions                                   | Test Conditions |        | Max. | Unit |

|-----------------|---------------------------------------------|---------------------------------------------------|-----------------|--------|------|------|

| V <sub>OH</sub> | Output HIGH Voltage                         | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4.0 mA |                 | 2.4    |      | V    |

| V <sub>OL</sub> | Output LOW Voltage                          | V <sub>CC</sub> = Min., I <sub>OL</sub> = 16.0 mA |                 |        | 0.4  | V    |

| V <sub>IH</sub> | Input HIGH Voltage                          |                                                   |                 | 2.0    |      | V    |

| V <sub>IL</sub> | Input LOW Voltage                           |                                                   |                 |        | 0.8  | V    |

| I <sub>IX</sub> | Input Current                               | $GND \le V_{IN} \le V_{CC}$                       |                 | -10    | +10  | μΑ   |

| V <sub>CD</sub> | Input Diode Clamp Voltage                   |                                                   |                 | Note 5 |      |      |

| I <sub>OZ</sub> | Output Leakage Current                      | $GND \leq V_{OUT} \leq V_{CC}$ , Output Disabled  |                 | -10    | +10  | μΑ   |

| I <sub>OS</sub> | Output Short Circuit Current <sup>[6]</sup> | V <sub>CC</sub> = Max., V <sub>OUT</sub> = GND    |                 | -20    | -90  | mA   |

| I <sub>CC</sub> | Power Supply Current                        | $V_{CC} = Max., V_{IN} = 2.0V,$                   | Com'l           |        | 80   | mA   |

|                 |                                             | I <sub>OUT</sub> = 0 mA<br>f=10 MHz               | Mil             |        | 100  |      |

| I <sub>SB</sub> | Standby Supply Current                      | Chip Enable Inactive,                             | Com'l           |        | 15   | mA   |

|                 |                                             | $\overline{CE} = V_{IH}, I_{OUT} = 0 \text{ mA}$  | Mil             |        | 15   |      |

## Capacitance<sup>[5]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                         | 10   | pF   |

Notes:

Contact a Cypress representative regarding industrial temperature range specification.

T<sub>A</sub> is the "instant on" case temperature.

See the last page of this specification for Group A subgroup testing information.

See the "Introduction to CMOS NVMs" section of the Cypress Data Book for general information on testing.

For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

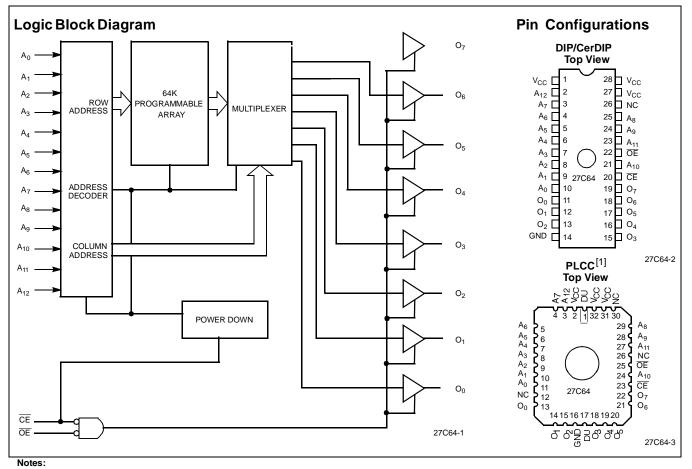

# AC Test Loads and Waveforms

#### Test Load

Equivalent to: THÉVENIN EQUIVALENT

OUTPUT O R<sub>TH</sub> 100Ω 2.0V

# Switching Characteristics Over the Operating $Range^{[2,3,5]}$

|                   |                                         | 2706 | 64-70 | 2706 | 64-90 | 27C64 | 1-120 | 27C64 | I-150 | 27C64 | 1-200 |      |

|-------------------|-----------------------------------------|------|-------|------|-------|-------|-------|-------|-------|-------|-------|------|

| Parameter         | Description                             | Min. | Max   | Min. | Max   | Min.  | Max   | Min.  | Max   | Min.  | Max   | Unit |

| t <sub>AA</sub>   | Address to Output Valid                 |      | 70    |      | 90    |       | 120   |       | 150   |       | 200   | ns   |

| t <sub>HZCE</sub> | Chip Enable Inactive to High Z          |      | 45    |      | 45    |       | 45    |       | 45    |       | 45    | ns   |

| t <sub>HZOE</sub> | Output Enable Inactive to High Z        |      | 25    |      | 25    |       | 30    |       | 30    |       | 30    | ns   |

| t <sub>OE</sub>   | Output Enable Active to Output<br>Valid |      | 40    |      | 40    |       | 50    |       | 50    |       | 50    | ns   |

| t <sub>CE</sub>   | Chip Enable Active to Output Valid      |      | 70    |      | 90    |       | 120   |       | 150   |       | 200   | ns   |

| t <sub>OH</sub>   | Data Hold from Address Change           | 3    |       | 3    |       | 3     |       | 3     |       | 3     |       | ns   |

| t <sub>PU</sub>   | Chip Enable Active to Power-Up          |      | 70    |      | 90    |       | 120   |       | 150   |       | 200   | ns   |

| t <sub>PD</sub>   | Chip Enable Inactive to<br>Power-Down   |      | 70    |      | 90    |       | 120   |       | 150   |       | 200   | ns   |

### **Erasure Characteristics**

Wavelengths of light less than 4000 angstroms begin to erase the devices in the windowed package. For this reason, an opaque label should be placed over the window if the EPROM is exposed to sunlight or fluorescent lighting for extended periods of time.

The recommended dose of ultraviolet light for erasure is a wavelength of 2537 angstroms for a minimum dose (UV intensity multiplied by exposure time) of 25 Wsec/cm2. For an ultraviolet lamp with a 12 mW/cm<sup>2</sup> power rating, the exposure time would be approximately 35 minutes. The CY27C64 needs to be within 1 inch of the lamp during erasure. Permanent damage may result if the

EPROM is exposed to high-intensity UV light for an extended period of time.

7258 Wsec/cm2 is the recommended maximum dosage.

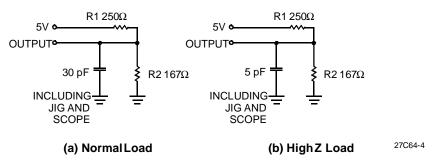

#### **Programming Modes**

Programming support is available from Cypress as well as from a number of third party software vendors. For detailed programming information, including a listing of software packages, please see the PROM Programming Information located at the end of this section. Programming algorithms can be obtained from any Cypress representative. When programming, select the Cypress CY7C266 algorithm.

#### Table 1. Mode Selection.

|          |                  |                  | Pin Function <sup>[7, 8]</sup> |                  |                  |                  |                  |                 |                                |

|----------|------------------|------------------|--------------------------------|------------------|------------------|------------------|------------------|-----------------|--------------------------------|

|          | Normal Operation | A <sub>8</sub>   | A <sub>9</sub>                 | A <sub>10</sub>  | A <sub>11</sub>  | A <sub>12</sub>  | CE               | OE              | $D_7 - D_0$                    |

| Mode     | Program          | VFY              | PGM                            | LAT              | NA               | NA               | CE               | V <sub>PP</sub> | $D_7 - D_0$                    |

| Read     |                  | A <sub>8</sub>   | A <sub>9</sub>                 | A <sub>10</sub>  | A <sub>11</sub>  | A <sub>12</sub>  | VIL              | V <sub>IL</sub> | O <sub>7</sub> -O <sub>0</sub> |

| Standby  | 1                | Х                | Х                              | Х                | Х                | Х                | V <sub>IH</sub>  | Х               | Three-Stated                   |

| Output E | Disable          | A <sub>8</sub>   | A <sub>9</sub>                 | A <sub>10</sub>  | A <sub>11</sub>  | A <sub>12</sub>  | V <sub>IL</sub>  | V <sub>IH</sub> | Three-Stated                   |

| Program  | ı                | V <sub>IHP</sub> | V <sub>ILP</sub>               | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>PP</sub> | $D_7 - D_0$                    |

| Program  | n Verify         | V <sub>ILP</sub> | V <sub>IHP</sub>               | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>PP</sub> | O <sub>7</sub> -O <sub>0</sub> |

| Program  | n Inhibit        | V <sub>IHP</sub> | V <sub>IHP</sub>               | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>PP</sub> | Three-Stated                   |

| Blank Cl | heck             | V <sub>ILP</sub> | V <sub>IHP</sub>               | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>PP</sub> | O <sub>7</sub> -O <sub>0</sub> |

Notes:

7. X = "don't care" but must not exceed V<sub>CC</sub> + 5%.

8. Address  $A_8 - A_{12}$  must be latched through lines  $A_0 - A_4$  in Programming modes.

#### Figure 1. Programming Pinout

27C64-5

27C64-6

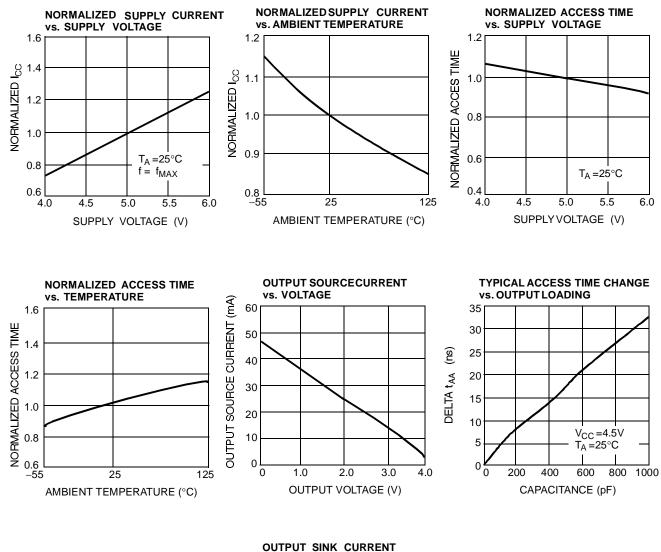

# Typical DC and AC Characteristics

# Ordering Information<sup>[9]</sup>

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|---------------|-----------------|-------------------------------------|--------------------|

| 70            | CY27C64-70JC  | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY27C64-70PC  | P15             | 28-Lead (600-Mil) Molded DIP        |                    |

|               | CY27C64-70WC  | W16             | 28-Lead (600-Mil) Windowed CerDIP   |                    |

| 90            | CY27C64-90JC  | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY27C64-90PC  | P15             | 28-Lead (600-Mil) Molded DIP        |                    |

|               | CY27C64-90WC  | W16             | 28-Lead (600-Mil) Windowed CerDIP   |                    |

| 120           | CY27C64-120JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY27C64-120PC | P15             | 28-Lead (600-Mil) Molded DIP        |                    |

|               | CY27C64-120WC | W16             | 28-Lead (600-Mil) Windowed CerDIP   |                    |

| 150           | CY27C64-150JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY27C64-150PC | P15             | 28-Lead (600-Mil) Molded DIP        |                    |

|               | CY27C64-150WC | W16             | 28-Lead (600-Mil) Windowed CerDIP   |                    |

| 200           | CY27C64-200JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY27C64-200PC | P15             | 28-Lead (600-Mil) Molded DIP        |                    |

|               | CY27C64-200WC | W16             | 28-Lead (600-Mil) Windowed CerDIP   |                    |

Notes:

9. Most of these products are available in industrial temperature range. Contact a Cypress representative for specifications and product availability.

#### MILITARY SPECIFICATIONS Group A Subgroup Testing

#### **DC Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| V <sub>OH</sub> | 1, 2, 3   |

| V <sub>OL</sub> | 1, 2, 3   |

| V <sub>IH</sub> | 1, 2, 3   |

| V <sub>IL</sub> | 1, 2, 3   |

| I <sub>IX</sub> | 1, 2, 3   |

| I <sub>OZ</sub> | 1, 2, 3   |

| I <sub>CC</sub> | 1, 2, 3   |

| I <sub>SB</sub> | 1, 2, 3   |

# **Switching Characteristics**

| Parameter       | Subgroups       |

|-----------------|-----------------|

| t <sub>AA</sub> | 7, 8, 9, 10, 11 |

| t <sub>OE</sub> | 7, 8, 9, 10, 11 |

| t <sub>CE</sub> | 7, 8, 9, 10, 11 |

Document #: 38-00448

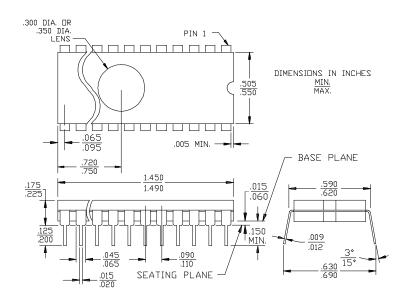

# Package Diagrams

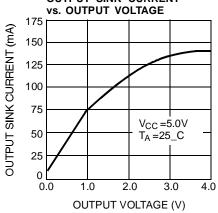

#### 32-Lead Plastic Leaded Chip Carrier J65

28-Lead (600-Mil) Molded DIP P15

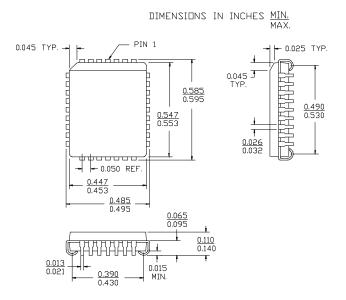

#### Package Diagrams (Continued)

#### 28-Lead (600-Mil) WindowedCerDIP W16 MIL-STD-1835 D40 Config.A

© Cypress Semiconductor Corporation, 1995. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of charges.